# **GD5F4GM8UEYIGR-MT**

DATASHEET (CASN Page Supported)

## **GD5F4GM8UEYIGR-MT**

# Contents

| FE/ | ATURE                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2  |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .4  | BLOCK DIAGRAM                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ME  | MORY MAPPING                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DE  | VICE OPERATION                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .1  | SPI Modes                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2  |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .3  |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .4  | Power Off Timing                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| co  | MMANDS DESCRIPTION                                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1   | WRITE ENABLE (WREN) (06H)                                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | · · · · · ·                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RE  |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .1  | Page Read                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2  | PAGE READ TO CACHE (13H)                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .3  | READ FROM CACHE (03H OR 0BH)                                                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .4  | READ FROM CACHE X2 (3BH)                                                                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .5  | READ FROM CACHE X4 (6BH)                                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .6  | READ FROM CACHE DUAL IO (BBH)                                                                      | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .7  | READ FROM CACHE QUAD IO (EBH)                                                                      | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .8  | READ FROM CACHE QUAD I/O DTR (EEH)                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .9  | READ ID (9FH)                                                                                      | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .10 | READ UID                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .11 | READ PARAMETER PAGE                                                                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .12 | READ CASN PAGE                                                                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PR  | OGRAM OPERATIONS                                                                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .1  | PAGE PROGRAM                                                                                       | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

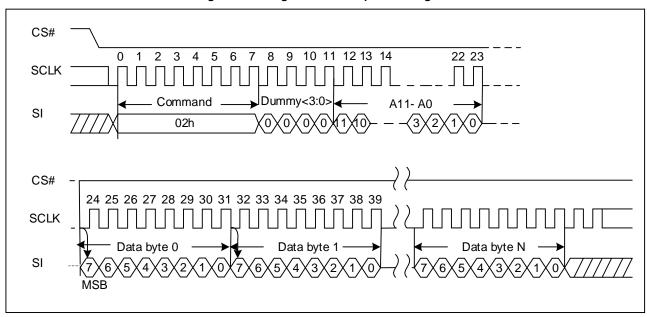

| .2  | Program Load (PL) (02H)                                                                            | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .3  | Program Load x4 (PL x4) (32H)                                                                      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

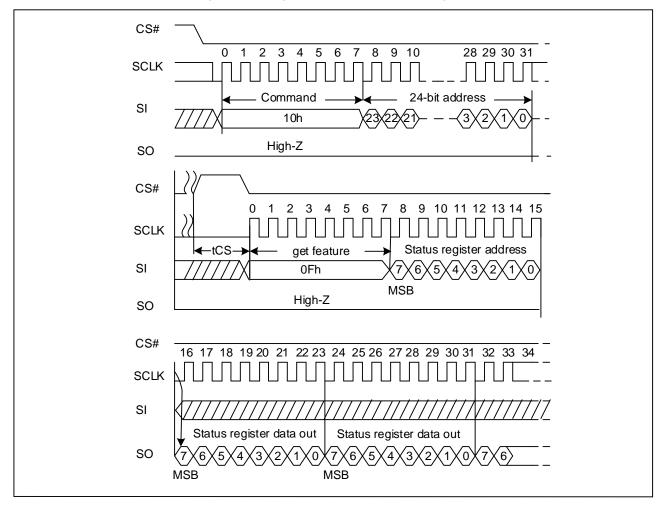

| .4  | PROGRAM EXECUTE (PE) (10H)                                                                         | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .5  | Internal Data Move                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .6  | Program Load Random Data (84h)                                                                     | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | GE .1 .2 .3 .4 ME AR DE .1 .2 .3 .4 CC WF .1 .2 .3 .4 .5 .6 .7 .8 .9 .10 .11 .12 PR .1 .2 .3 .4 .5 | 2 CONNECTION DIAGRAM .3 PIN DESCRIPTION4 BLOCK DIAGRAM .4 MEMORY MAPPING. ARRAY ORGANIZATION5 PI MODES2 HOLD MODE3 WRITE PROTECTION4 POWER OFF TIMING6 COMMANDS DESCRIPTION. WRITE OPERATIONS1 WRITE ENABLE (WREN) (06H)2 WRITE DISABLE (WREN) (04H). READ OPERATIONS1 PAGE READ2 PAGE READ TO CACHE (13H)3 READ FROM CACHE (03H OR 0BH)4 READ FROM CACHE (03H OR 0BH)5 READ FROM CACHE (04H OR 0BH)6 READ FROM CACHE (04H OR 0BH)7 READ FROM CACHE (04H OR 0BH)8 READ FROM CACHE QUAD IO (EBH)8 READ FROM CACHE QUAD IO (EBH)9 READ ID (9FH)10 READ UID11 READ PARAMETER PAGE12 READ CASN PAGE PROGRAM OPERATIONS1 PAGE PROGRAM2 PROGRAM LOAD (PL) (02H)3 PROGRAM LOAD (PL) (02H)3 PROGRAM LOAD (PL) (02H)3 PROGRAM LOAD (PL) (02H)3 PROGRAM LOAD (PL) (02H)4 PROGRAM EXECUTE (PE) (10H). |

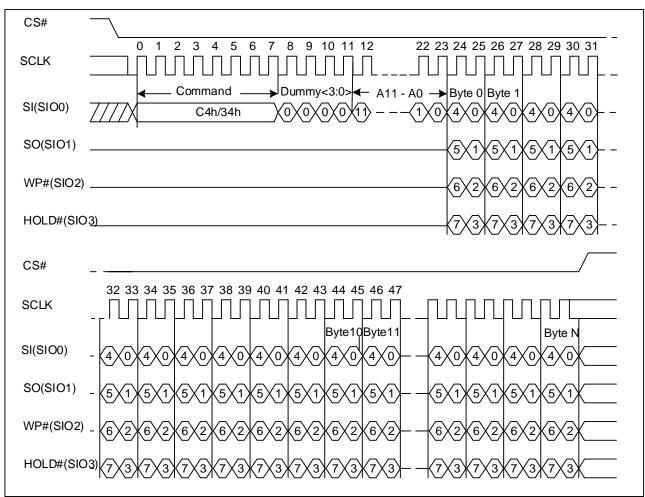

|    | 9.7  | Program Load Random Data x4 (C4h/34h)                | 47 |

|----|------|------------------------------------------------------|----|

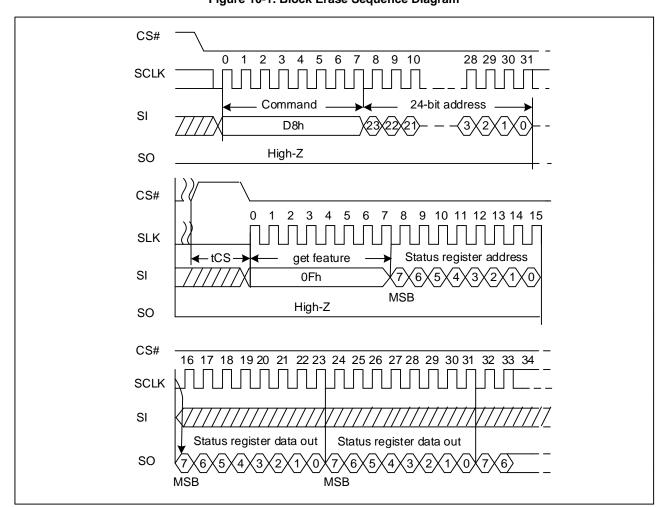

| 10 | ER   | ASE OPERATIONS                                       | 48 |

|    | 10.1 | BLOCK ERASE (D8H)                                    | 48 |

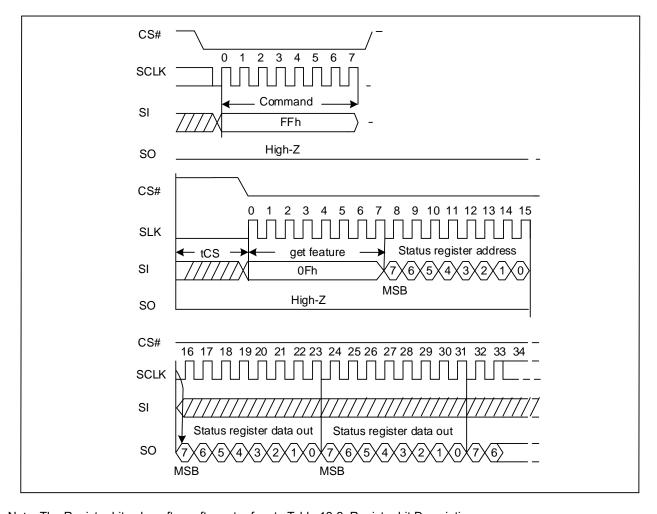

| 11 | RE   | SET OPERATIONS                                       | 49 |

|    | 11.1 | SOFT RESET (FFH)                                     | 49 |

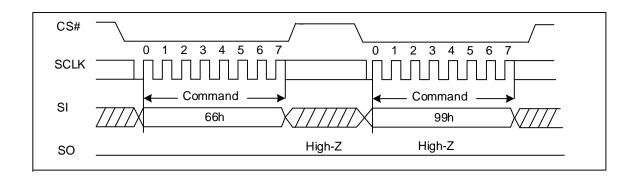

|    | 11.2 | ENABLE POWER ON RESET (66H) AND POWER ON RESET (99H) | 50 |

| 12 | FE   | ATURE OPERATIONS                                     | 51 |

|    | 12.1 | GET FEATURES (0FH) AND SET FEATURES (1FH)            | 51 |

|    | 12.2 | STATUS REGISTER AND DRIVER REGISTER                  | 55 |

|    | 12.3 | OTP REGION                                           | 56 |

|    | 12.4 | ASSISTANT BAD BLOCK MANAGEMENT                       | 57 |

|    | 12.5 | BLOCK PROTECTION                                     | 58 |

|    | 12.6 | POWER LOCK DOWN PROTECTION                           |    |

|    | 12.7 | Internal ECC                                         | 60 |

| 13 | РО   | WER ON/OFF TIMING                                    | 62 |

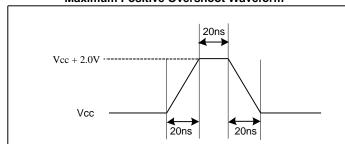

| 14 | АВ   | SOLUTE MAXIMUM RATINGS                               | 63 |

| 15 | CA   | PACITANCE MEASUREMENT CONDITIONS                     | 64 |

| 16 | DC   | CHARACTERISTIC                                       | 65 |

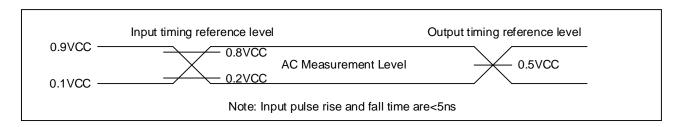

| 17 | AC   | CHARACTERISTICS                                      | 66 |

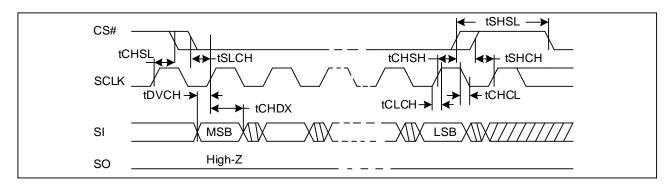

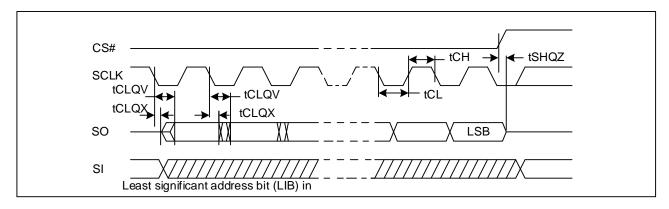

| 18 | PE   | RRFORMANCE AND TIMING                                | 67 |

| 19 | OR   | DERING INFORMATION                                   | 69 |

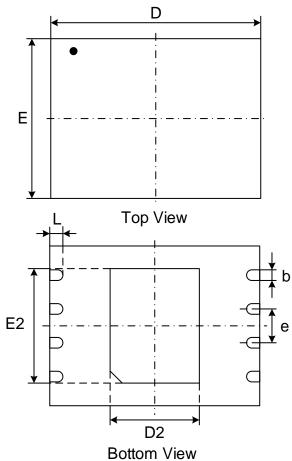

| 20 | PA   | CKAGE INFORMATION                                    | 70 |

| 24 | DE   | VISION HISTORY                                       | 71 |

### 1 FEATURE

- ◆ 4Gb SLC NAND Flash

- ◆ Page Size

- Internal ECC On (ECC\_EN=1, default):

Page Size: 2048-Byte+64-Byte

- Internal ECC Off (ECC\_EN=0):

Page Size: 2048-Byte+128-Byte

- ◆ Standard, Dual, Quad SPI,DTR

- Standard SPI: SCLK, CS#, SI, SO, WP#, HOLD#

- Dual SPI: SCLK, CS#, SIO0, SIO1, WP#, HOLD#

- Quad SPI: SCLK, CS#, SIO0, SIO1, SIO2, SIO3

- DTR(Double Transfer Rate) Read : SCLK, CS#, SIO0,

SIO1, SIO2, SIO3

- ◆ High Speed Clock Frequency

- 3.3V:

133MHz for Standard/Dual/Quad SPI 104MHz for DTR Quad SPI

- ◆ Software/Hardware Write Protection

- Write protect all/portion of memory via software

- Register protection with WP# Pin

- Power Lock Down Protection

- ◆ Single Power Supply Voltage

- Full voltage range for 3.3V: 2.7V  $\sim$  3.6V

- Advanced security Features

- 20K-Byte OTP Region

- ◆ Program/Erase/Read Speed

- Page Program time: 320us typical- Block Erase time: 3ms typical

- Page read time: 120us maximum

- ◆ Low Power Consumption

- 30mA maximum active current

- 100uA maximum standby current

- ◆ Enhanced access performance

- 2Kbyte cache for fast random read

- ◆ Advanced Feature for NAND

- Factory good block0

- Reliability

- P/E cycles with ECC: Typical 80K(2)

- Data retention: 10 Years

- ◆ Internal ECC

- 8bits /528byte

Note: 1. ECC is On as default, and it can be disabled by the user.

2. The P/E cycles with ECC will be 60K at 105°C operation temperature.

## 2 GENERAL DESCRIPTION

SPI (Serial Peripheral Interface) NAND Flash provides an ultra-cost effective while high density non-volatile memory storage solution for embedded systems, based on an industry-standard NAND Flash memory core. It is an attractive alternative to SPI-NOR and standard parallel NAND Flash, with advanced features, Total pin count is 8, including VCC and GND

- · Density is 4Gb

- · Superior write performance and cost per bit over SPI-NOR

- · Significant low cost than parallel NAND

This low-pin-count NAND Flash memory follows the industry-standard serial peripheral interface, and always remains the same pin out from one density to another. The command sets resemble common SPI-NOR command sets, modified to handle NAND specific functions and added new features. GigaDevice SPI NAND is an easy-to-integrate NAND Flash memory, with specified designed features to ease host management:

- **User-selectable internal ECC**. ECC parity is generated internally during a page program operation. When a page is read to the cache register, the ECC parity is detected and corrects the errors when necessary. The 64-bytes spare area is available even when internal ECC enabled. The device outputs corrected data and returns an ECC error status.

- Internal data move or copy back with internal ECC. The device can be easily refreshed and manage garbage collection task, without need of shift in and out of data. This command string can only be used on blocks with the same parity attribute.

- Power on Read with internal ECC. The device will automatically read first page of first block to cache after power on, then host can directly read data from cache for easy boot. Also the data is promised correct by internal ECC when ECC enabled.

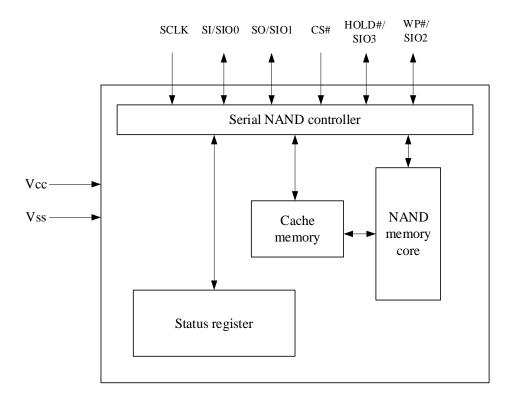

It is programmed and read in page-based operations, and erased in block-based operations. Data is transferred to or from the NAND Flash memory array, page by page, to a data register and a cache register. The cache register is closest to I/O control circuits and acts as a data buffer for the I/O data; the data register is closest to the memory array and acts as a data buffer for the NAND Flash memory array operation. The cache register functions as the buffer memory to enable page and random data READ/WRITE and copy back operations. These devices also use a SPI status register that reports the status of device operation.

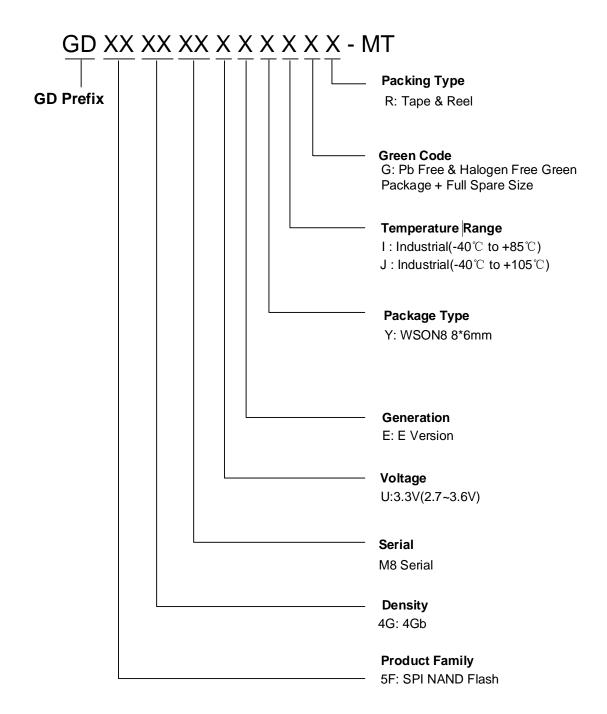

## 2.1 VALID PART NUMBERS

Please contact GigaDevice regional sales for the latest product selection and available form factors

| Product Number    | Density | Voltage      | Package Type | Temperature |

|-------------------|---------|--------------|--------------|-------------|

| GD5F4GM8UEYIGR-MT | 4Gbit   | 2.7V to 3.6V | WSON8(8*6mm) | -40℃ to 85℃ |

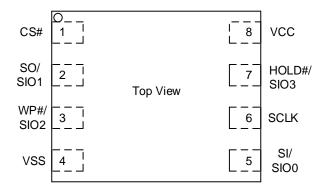

## 2.2 CONNECTION DIAGRAM

Figure 2-1. Connect Diagram

8 - LEAD WSON

### 2.3 PIN DESCRIPTION

| Pin Name    | I/O    | Description                                                     |

|-------------|--------|-----------------------------------------------------------------|

|             |        |                                                                 |

| CS#         | I      | Chip Select input, active low                                   |

| SO/SIO1     | I/O    | Serial Data Output / Serial Data Input Output 1                 |

| WP#/SIO2    | I/O    | Write Protect, active low / Serial Data Input Output 2          |

| VSS         | Ground | Ground                                                          |

| SI/SIO0     | I/O    | Serial Data Input / Serial Data Input Output 0                  |

| SCLK        | I      | Serial Clock input                                              |

| HOLD# /SIO3 | I/O    | Hold Input/Serial Data Input Output 3                           |

| VCC         | Supply | Power Supply                                                    |

| NC          |        | Not Connect, Not internal connection; can be driven or floated. |

### Note:

- 1. CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

- 2. If WP# and HOLD# are unused, they must be driven high by the host, or an external pull-up resistor must be placed on the PCB in order to avoid allowing WP# and HOLD# input to float.

## 2.4 BLOCK DIAGRAM

Figure 2-2. Block Diagram

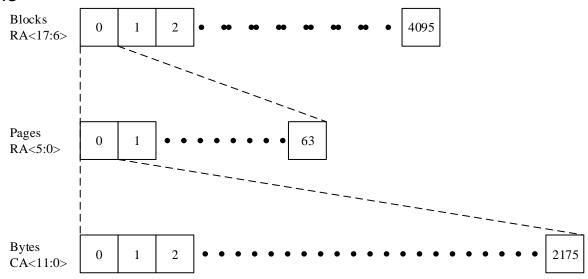

## 3 MEMORY MAPPING

### For 4G

#### Note:

- CA: Column Address. The 12-bit address is capable of addressing from 0 to 4095 bytes; however, only bytes 0 through 2175/2111 are valid. Bytes 2176/2112 through 4095 of each page are "out of bounds," do not exist in the device, and cannot be addressed.

- 2. RA: Row Address. RA<5:0>selects a page inside a block, and RA<17:6>selects a block.

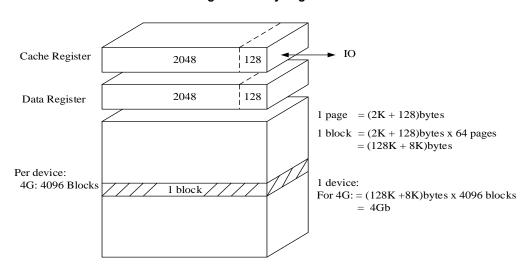

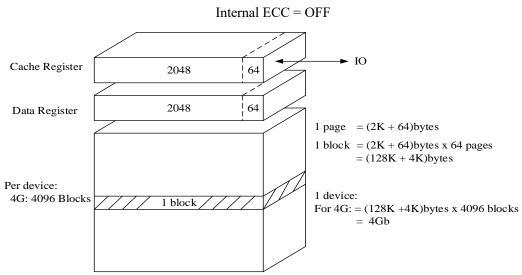

## **4** ARRAY ORGANIZATION

| Table | 4. Array | Organ | ization |

|-------|----------|-------|---------|

|-------|----------|-------|---------|

| Each device has | Each block has | Each page has |        |

|-----------------|----------------|---------------|--------|

| 4Gb             |                |               |        |

| 512M+32M        | 128K+8K        | 2K+128        | bytes  |

| 4096 x 64       | 64             | -             | pages  |

| 4096            | -              | -             | blocks |

Figure 4. Array Organization

Internal ECC = ON

#### Note:

- 1.When Internal ECC is enabled, user can program the first 64 bytes of the entire 128 bytes spare area and the last 64 bytes of the whole spare area cannot be programed, user can read the entire 128 Byte spare area.

- 2. When Internal ECC is disabled, user can read and program the entire 128 bytes spare area.

## 5 DEVICE OPERATION

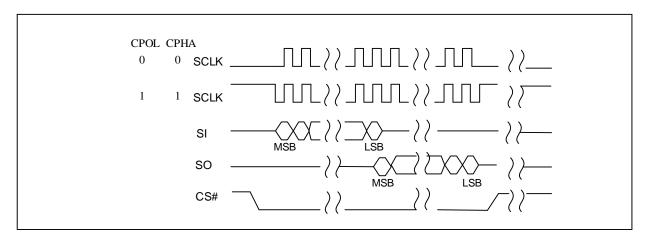

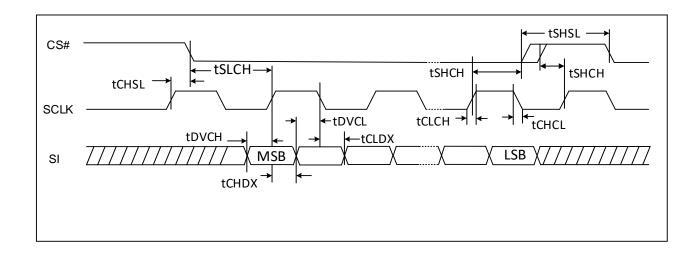

### 5.1 SPI Modes

SPI NAND supports two SPI modes:

- CPOL = 0, CPHA = 0 (Mode 0)

- CPOL = 1, CPHA = 1 (Mode 3)

Input data is latched on the rising edge of SCLK and data shifts out on the falling edge of SCLK for both modes. All timing diagrams shown in this data sheet are mode 0. See Figure 5-1 for more details.

Figure 5-1. SPI Modes Sequence Diagram

Note: While CS# is HIGH, keep SCLK at VCC or GND (determined by mode 0 or mode 3). Do not toggle SCLK until CS# is driven LOW.

We recommend that the user pull CS# to high when user don't use SPI flash, otherwise it is not good for flash. When CS# is high and SCLK at VCC or GND state, the device is in idle state.

### Standard SPI

SPI NAND Flash features a standard serial peripheral interface on 4 signals bus: Serial Clock (SCLK), Chip Select (CS#), Serial Data Input (SI) and Serial Data Output (SO).

### **Dual SPI**

SPI NAND Flash supports Dual SPI operation when using the x2 and dual IO commands. These commands allow data to be transferred to or from the device at two times the rate of the standard SPI. When using the Dual SPI command the SI and SO pins become bidirectional I/O pins: SIO0 and SIO1.

### **Quad SPI**

SPI NAND Flash supports Quad SPI operation when using the x4 and Quad IO commands. These commands allow data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command the SI and SO pins become bidirectional I/O pins: SIO0 and SIO1, and WP# and HOLD# pins become SIO2 and SIO3.

#### **DTR Quad SPI**

The device supports DTR Quad SPI operation when using the "DTR Quad I/O Fast Read" command.

These command allow data to be transferred to or from the device at eight times the rate of the standard SPI, and data output will be latched on both rising and falling edges of the serial clock. When using the DTR Quad SPI command the SI and SO pins become bidirectional I/O pins: IO0 and IO1, and WP# and HOLD# pins become IO2 and IO3. DTR Quad SPI commands require the Quad Enable bit (QE) in Status Register to be enable.

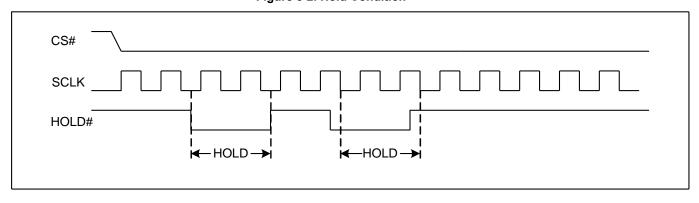

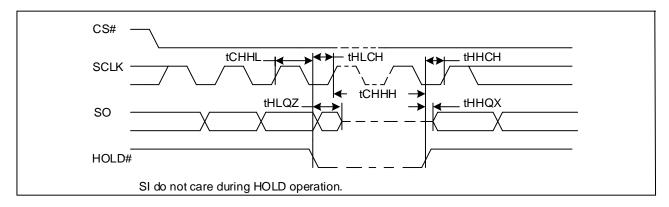

## 5.2 HOLD Mode

The HOLD# function is only available when QE=0, If QE=1, The HOLD# functions is disabled, the pin acts as dedicated data I/O pin.

The HOLD# signal goes low to stop any serial communications with the device, but doesn't stop the operation of reading, programming, or erasing in progress.

The operation of HOLD, need CS# keep low, and starts on falling edge of the HOLD# signal, with SCLK signal being low (if SCLK is not being low, HOLD operation will not start until SCLK being low). The HOLD condition ends on rising edge of HOLD# signal with SCLK being low (If SCLK is not being low, HOLD operation will not end until SCLK being low).

The SO is high impedance, both SI and SCLK don't care during the HOLD operation, if CS# drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and then CS# must be at low.

Figure 5-2. Hold Condition

### 5.3 Write Protection

SPI NAND provides Hardware Protection Mode besides the Software Mode. Write Protect (WP#) prevents the block lock bits (BP0, BP1, BP2 and INV, CMP) from being over written. If the BRWD bit is set to 1 and WP# is LOW, the block protect bits cannot be altered.

To enable the Write Protection, the Quad Enable bit (QE) of feature (B0[0]) must be set to 0.

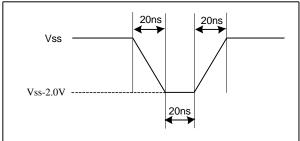

# **5.4** Power Off Timing

Please do not turn off the power before Write/Erase operation is completed. Avoid using the device when the battery is low. Power shortage and/or power failure before Write/Erase operation is complete will cause loss of data and/or damage to data.

# **6** COMMANDS DESCRIPTION

Table 6-1. Commands Set

| Command Name                       | Byte1                  | Byte2   | Byte3                | Byte4                  | Byte5                | Byte6                      | Byte 7 |

|------------------------------------|------------------------|---------|----------------------|------------------------|----------------------|----------------------------|--------|

| Write Enable                       | 06h                    |         |                      |                        |                      |                            |        |

| Write Disable                      | 04h                    |         |                      |                        |                      |                            |        |

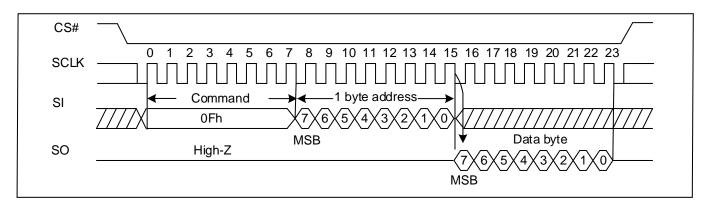

| Get Features                       | 0Fh                    | A7-A0   | D7-D0                | Wrap <sup>(7)</sup>    |                      |                            |        |

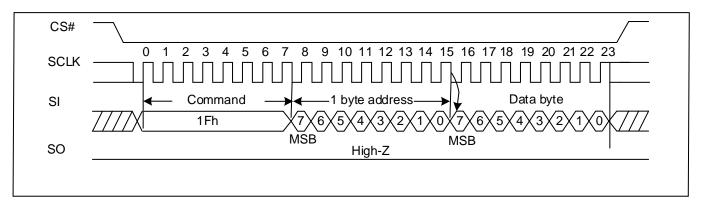

| Set Feature                        | 1Fh                    | A7-A0   | D7-D0                |                        |                      |                            |        |

| Page Read (to cache)               | 13h                    | A23-A16 | A15-A8               | A7-A0                  |                      |                            |        |

| Read From Cache                    | 03h/0Bh <sup>(9)</sup> | A15-A8  | A7-A0 <sup>(2)</sup> | Dummy <sup>(1)</sup>   | D7-D0                |                            |        |

| Read From Cache x 2                | 3Bh <sup>(9)</sup>     | A15-A8  | A7-A0 <sup>(2)</sup> | Dummy <sup>(1)</sup>   | D7-D0                |                            |        |

| Read From Cache x 4                | 6Bh <sup>(9)</sup>     | A15-A8  | A7-A0 <sup>(2)</sup> | Dummy <sup>(1)</sup>   | D7-D0                |                            |        |

| Read From Cache Dual IO            | BBh                    | A15-A8  | A7-A0 <sup>(2)</sup> | Dummy <sup>(1)</sup>   | D7-D0                |                            |        |

| Read From Cache Quad IO            | EBh                    | A15-A8  | A7-A0 <sup>(2)</sup> | Dummyx2 <sup>(1)</sup> | D7-D0                |                            |        |

| Read From Cache Quad I/O<br>DTR    | EEh                    | A31-A24 | A23-A16              | A15-A8                 | A7-A0 <sup>(2)</sup> | Dummy<br>x8 <sup>(1)</sup> | D7-D0  |

| Read ID <sup>(4)</sup>             | 9Fh                    | Dummy   | MID                  | DID                    |                      |                            |        |

| Read parameter page <sup>(8)</sup> | 13h                    | 00h     | 00h                  | 01h                    |                      |                            |        |

| Read UID <sup>(8)</sup>            | 13h                    | 00h     | 00h                  | 00h                    |                      |                            |        |

| Program Load                       | 02h                    | A15-A8  | A7-A0 <sup>(3)</sup> | D7-D0                  | Next byte            |                            |        |

| Program Load x4                    | 32h                    | A15-A8  | A7-A0 <sup>(3)</sup> | D7-D0                  | Next byte            |                            |        |

| Program Execute                    | 10h                    | A23-A16 | A15-A8               | A7-A0                  |                      |                            |        |

| Program Load Random Data           | 84h                    | A15-A8  | A7-A0 <sup>(3)</sup> | D7-D0                  | Next byte            |                            |        |

| Program Load Random Data x4        | C4h/34h                | A15-A8  | A7-A0 <sup>(3)</sup> | D7-D0                  | Next byte            |                            |        |

| Block Erase(128K)                  | D8h                    | A23-A16 | A15-A8               | A7-A0                  |                      |                            |        |

| Reset <sup>(5)</sup>               | FFh                    |         | _                    |                        |                      |                            |        |

| Enable Power on Reset              | 66h                    |         |                      |                        |                      |                            |        |

| Power on Reset <sup>(6)</sup>      | 99h                    |         |                      |                        |                      |                            |        |

#### Note:

1. 03h/0Bh/3Bh/6Bh has 8 clock, 1 byte dummy.

BBh has 4 clock, 1 byte dummy.

EBh has 4 clock, 2 bytes dummy.

EEh has 8 clock, 8 bytes dummy.

2. The A15-A0 (03h/0Bh/3Bh/6Bh) has 16 clock, include 4 clock dummy.

The A15-A0 (BBh) has 8 clock, include 2 clock dummy.

The A15-A0 (EBh) has 4 clock, include 1 clock dummy.

The A31-A0 (EEh) has 4 clock, include 2.5 clock dummy.

- 3. The A15-A0 has 16 clock, include 4 clock dummy.

- 4. MID is Manufacture ID (C8h for GigaDevice), DID is Device ID.

- 5. Reset command:

- Reset will reset PAGE READ/PROGRAM/ERASE operation.

- Reset will reset status register bits P\_FAIL/E\_FAIL/WEL/OIP/ECCS/ECCSE.

- 6. Power on reset:

Retrieve status register and data in cache to power on status.

- 7. The output would be updated by real-time, until CS# is driven high.

- 8. Read UID/parameter page are same as page read to cache.

## 7 WRITE OPERATIONS

# 7.1 Write Enable (WREN) (06h)

The Write Enable (WREN) command is for setting the Write Enable Latch (WEL) bit. The Write Enable Latch (WEL) bit must be set prior to following operations that change the contents of the memory array:

- Page program

- OTP program/OTP protection

- Block erase

The WEL bit can be cleared after a reset command.

SCLK 0 1 2 3 4 5 6 7

SCLK Command Command High-Z

Figure 7-1. Write Enable Sequence Diagram

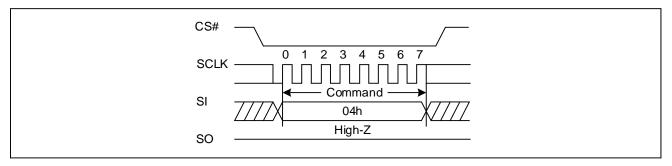

# 7.2 Write Disable (WRDI) (04h)

The Write Disable command is for resetting the Write Enable Latch (WEL) bit. The WEL bit is reset by following condition:

- Page program

- OTP program/OTP protection

- Block erase

Figure 7-2. Write Disable Sequence Diagram

## **8** READ OPERATIONS

## 8.1 Page Read

The PAGE READ (13h) command transfers the data from the NAND Flash array to the cache register. The command sequence is as follows:

- 13h (PAGE READ to cache)

- 0Fh (GET FEATURES command to read the status)

- 03h or 0Bh (Read from cache)/3Bh (Read from cache x2)/6Bh (Read from cache x4)/BBh (Read from cache dual IO)/EBh (Read from cache Quad IO)/EBh (Read from cache X2)/6Bh (Read from cache X4)/BBh (Read from cache X4)/

The PAGE READ command requires a 24-bit address. After the block/page addresses are registered, the device starts the transfer from the main array to the cache register, and is busy for tRD time. During this time, the GET FEATURE (0Fh) command can be issued to monitor the status. Followed the page read operation, the RANDOM DATA READ (03h/0Bh/3Bh/6Bh/BBh/EBh) command must be issued in order to read out the data from cache. The output data starts at the initial address specified in the command, once it reaches the ending boundary of whole page section, the output will wrap around from the beginning boundary until CS# is pulled high to terminate this operation. Refer waveforms to view the entire READ operation.

Note:(1) The command 6Bh (Read from cache x4)/EBh (Read from cache Quad IO)/EEh (Read from cache Quad IO DTR) is only available with the QE enable.

(2) When user read to the end of 64-Byte spare area, it won't wrap around from the beginning boundary and an additional 64Byte ECC code will be read. (Internal ECC enabled)

16

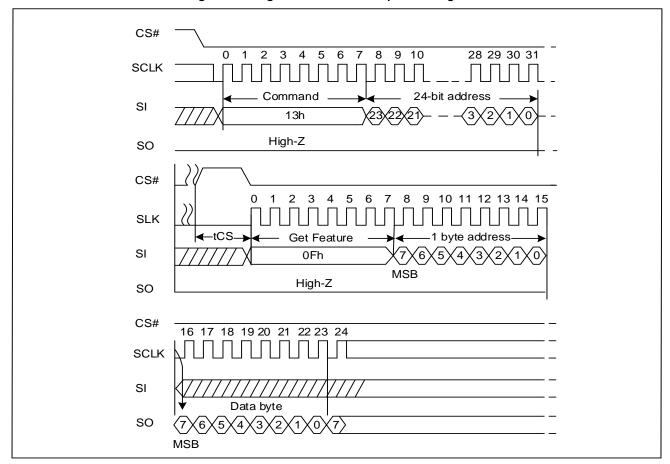

# 8.2 Page Read to Cache (13h)

The command page read to cache is read the data from flash array to cache register.

Figure 8-1. Page Read to cache Sequence Diagram

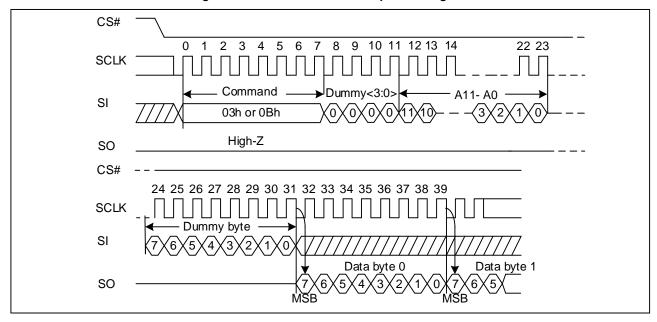

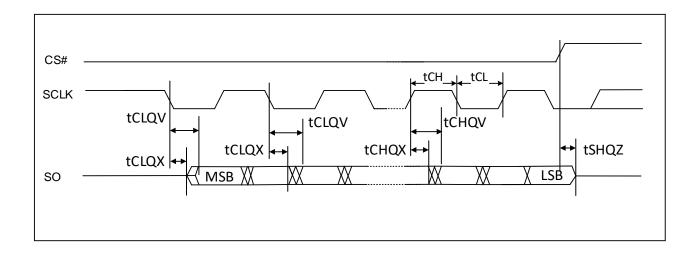

# 8.3 Read From Cache (03h or 0Bh)

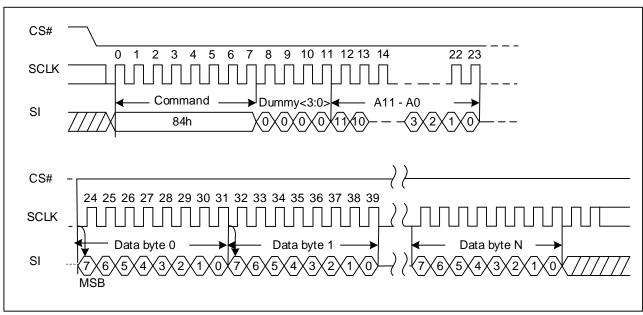

The command sequence is shown below.

Figure 8-2. Read From Cache Sequence Diagram

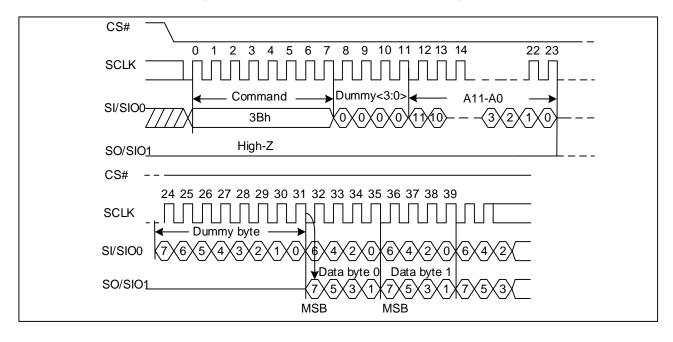

# 8.4 Read From Cache x2 (3Bh)

The command sequence is shown below.

Figure 8-3. Read From Cache x2 Sequence Diagram

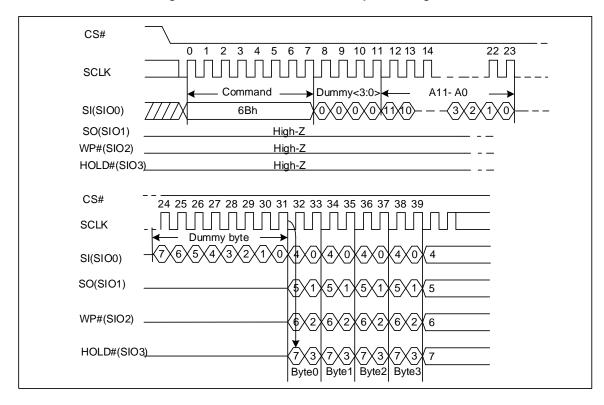

## 8.5 Read From Cache x4 (6Bh)

The Quad Enable bit (QE) of feature (B0[0]) must be set to enable the read from cache x4 command. The command sequence is shown below.

Figure 8-4. Read From Cache x4 Sequence Diagram

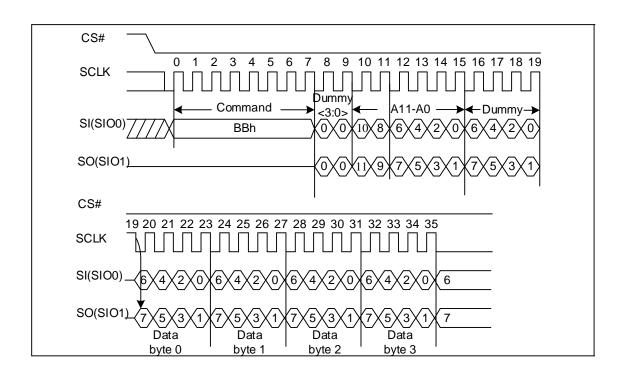

## 8.6 Read From Cache Dual IO (BBh)

The Read from Cache Dual I/O command (BBh) is similar to the Read form Cache x2 command (3Bh) but with the capability to input the 4 Dummy bits, followed by a 12-bit column address for the starting byte address and 4 clock dummy by SIO0 and SIO1, each bit being latched in during the rising edge of SCLK, then the cache contents are shifted out 2-bit per clock cycle from SIO0 and SIO1. The first address byte can be at any location. The address increments automatically to the next higher address after each byte of data shifted out until the boundary wrap bit.

Figure 8-5. Read From Cache Dual IO Sequence Diagram

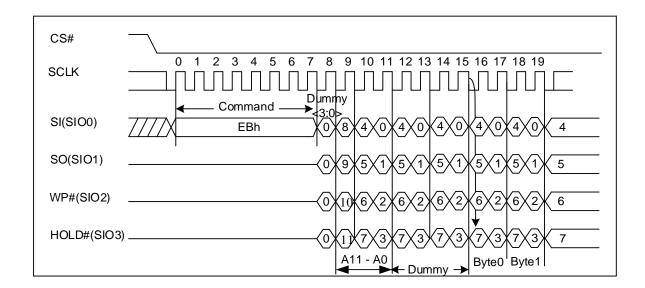

## 8.7 Read From Cache Quad IO (EBh)

The Read from Cache Quad IO command is similar to the Read from Cache x4 command but with the capability to input the 4 dummy bits, followed a 12-bit column address for the starting byte address and a dummy byte by SIO0, SIO1, SIO3, SIO4, each bit being latched in during the rising edge of SCLK, then the cache contents are shifted out 4-bit per clock cycle from SIO0, SIO1, SIO2, SIO3. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out until the boundary wrap bit. The Quad Enable bit (QE) of feature (B0[0]) must be set to enable the read from cache quad IO command.

Figure 8-6. Read From Cache Quad IO Sequence Diagram

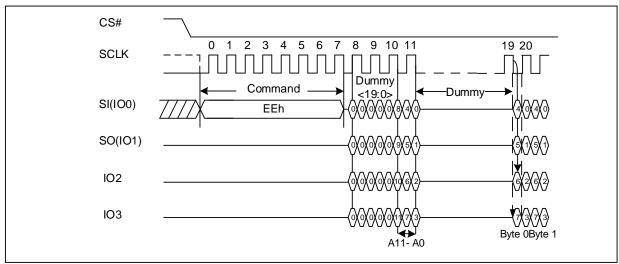

## 8.8 Read From Cache Quad I/O DTR (EEh)

The DTR Quad IO command enables Double Transfer Rate throughput on quad I/O of Serial Flash in read mode. A Quad Enable (QE) bit of status Register must be set to "1" before sending the DTR Quad IO command. The address (interleave on 4 I/O pins) is latched on both rising and falling edge of SCLK, and data (interleave on 4 I/O pins) shift out on both rising and falling edge of SCLK. The 8-bit address can be latched-in at one clock, and 8-bit data can be read out at one clock, which means four bits at rising edge of clock, the other four bits at falling edge of clock.

The first address Byte can be at any location. The address is automatically increased to the next higher address after each Byte data is shifted out, so the whole page can be read out at a single DTR Quad IO command. The address counter rolls over to 0 when the highest address has been reached.

Figure 8-7. Read From Cache Quad I/O DTR Sequence Diagram

Note:

Please contact GigaDevice when there is a need to use the EEh command for DTR.

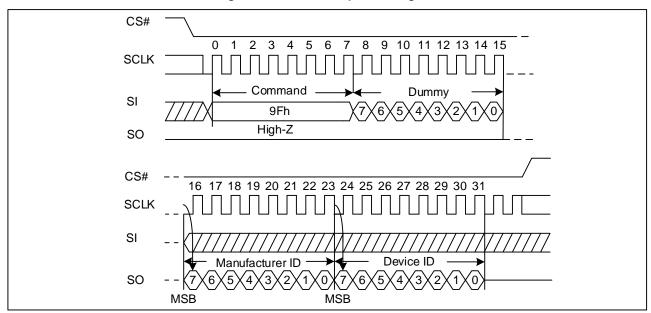

# 8.9 Read ID (9Fh)

The READ ID command is used to identify the NAND Flash device.

• The READ ID command outputs the Manufacturer ID and the device ID. See Table 8-1 for details.

Figure 8-8. Read ID Sequence Diagram

Table 8-1. READ ID Table

| Part No    | MID | DID1 |

|------------|-----|------|

| GD5F4GM8UE | C8h | 95h  |

### 8.10 Read UID

The Read Unique ID function is used to retrieve the 16 bytes unique ID (UID) for the device. The unique ID when combined with the device manufacturer shall be unique.

The UID data may be stored within the Flash array. To allow the host to determine if the UID is without bit errors, the UID is returned with its complement. If the XOR of the UID and its bit-wise complement is all ones, then the UID is valid. To accommodate robust retrieval of the UID in the case of bit errors, sixteen copies of the UID and the corresponding complement are stored by the target. For example, reading bytes 32-63 returns to the host another copy of the UID and its complement.

| Bytes | Value                     |

|-------|---------------------------|

| 0-15  | UID                       |

| 16-31 | UID complement (bit-wise) |

#### Sequence is as follows:

- 1. Use Set Feature command to set B0 register, to enable OTP\_EN.

- 2. Use Get Feature command to get data from B0 register and check if the OTP\_EN is enable.

- 3. Use page read to cache (13h) command with address 24'h000000h, read data from array to cache.

- 4. Use 0Fh (GET FEATURES command) read the status.

- 5. User can use Read from cache command (03h/0Bh), read 16 bytes UID from cache.

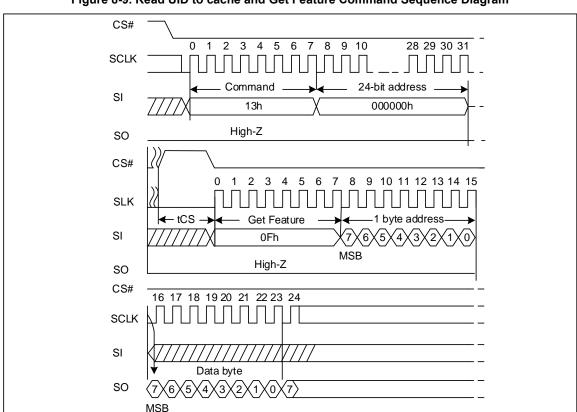

Figure 8-9. Read UID to cache and Get Feature Command Sequence Diagram

## 8.11 Read Parameter Page

The Read Parameter Page function retrieves the data structure that describes the chip's organization, features, timing and other behavioral parameters. This data structure enables the host processor to automatically recognize the SPI-NAND Flash configuration of a device. The whole data structure is repeated at least three times. The Read from Cache command can be issued during execution of the read parameter page to read specific portion-soft the parameter page.

### Sequence is as follows:

- 1. Use Set Feature command to set B0h register, to enable OTP\_EN.

- 2. Use Get Feature command to get data from B0 register and check if the OTP\_EN is enable.

- 3. Use Page Read to Cache (13h) command with address 24'h000001h. Load parameter page from array to cache.

- 4. Use 0Fh (GET FEATURES command) read the status

- 5. User can use Read from cache command (03h/0Bh), read parameter page from cache from Byte0 to Byte767.

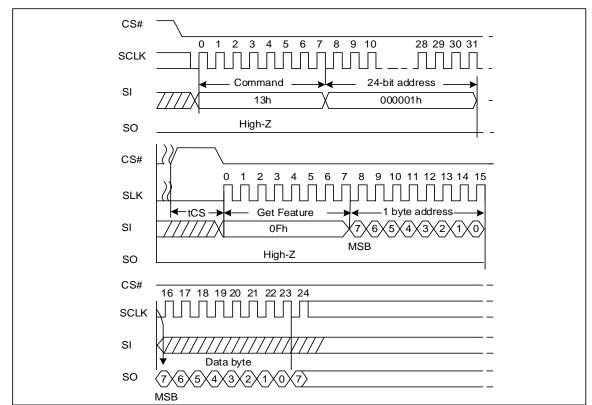

Figure 8-10. Read parameter page to cache and Get Feature Command Sequence Diagram

# **GD5F4GM8UEYIGR-MT**

### Parameter page table as follow (4G)

| Byte  | O/M | Description                  |                    |             | 3.3V |

|-------|-----|------------------------------|--------------------|-------------|------|

| 0-3   | М   | Parameter page signature     |                    |             | 4Fh  |

|       |     | Byte 0: 4Fh, "O"             |                    |             | 4Eh  |

|       |     | Byte 1: 4Eh, "N"             |                    |             | 46h  |

|       |     | Byte 2: 46h, "F"             |                    |             | 49h  |

|       |     | Byte 3: 49h, "I"             |                    |             |      |

| 4-5   | М   | Revision number              |                    |             | 00h  |

|       |     | 0-15 Reserved (0)            |                    |             | 00h  |

| 6-7   | М   | Features supported           |                    |             | 00h  |

|       |     | 0-15 Reserved (0)            |                    |             | 00h  |

| 8-9   | М   | Reserved (0)                 |                    |             | 00h  |

|       |     |                              |                    |             | 00h  |

| 10-31 |     | Reserved (0)                 |                    |             | 00h  |

|       |     |                              |                    |             |      |

|       |     |                              |                    |             | 00h  |

|       |     | Manufacturer Information blo | ock                |             |      |

| 32-43 | М   | Device manufacturer (12 AS   | CII characters)"GI | GADEVICE "  | 47h  |

|       |     |                              |                    |             | 49h  |

|       |     |                              |                    |             | 47h  |

|       |     |                              |                    |             | 41h  |

|       |     |                              |                    |             | 44h  |

|       |     |                              |                    |             | 45h  |

|       |     |                              |                    |             | 56h  |

|       |     |                              |                    |             | 49h  |

|       |     |                              |                    |             | 43h  |

|       |     |                              |                    |             | 45h  |

|       |     |                              |                    |             | 20h  |

|       |     |                              |                    |             | 20h  |

| 44-63 | М   | Device model (20 ASCII cha   | racters)           |             | 47h  |

|       |     | Device Model O               | RGANIZATION        | VCC RANGE   | 44h  |

|       |     | "GD5F4GM8U" X                | 4                  | 2.7v ~ 3.6v | 35h  |

|       |     |                              |                    |             | 46h  |

|       |     |                              |                    |             | 34h  |

|       |     |                              |                    |             | 47h  |

|       |     |                              |                    |             | 4Dh  |

|       |     |                              |                    |             | 38h  |

|       |     |                              |                    |             | 55h  |

|       |     |                              |                    |             | 20h  |

| algabevi |   | OI I-MAND                                      | ODSI TOMOGETTON-MIT |

|----------|---|------------------------------------------------|---------------------|

|          |   |                                                | 20h                 |

| 64       | М | JEDEC manufacturer ID"C8"                      | C8h                 |

| 65-66    | 0 | Date code                                      | 00h                 |

|          |   |                                                | 00h                 |

| 67-79    |   | Reserved                                       | 00h                 |

|          |   |                                                | 00h                 |

|          |   |                                                | 00h                 |

|          |   | Memory organization block                      |                     |

| 80-83    | М | Number of data bytes per page                  | 00h                 |

|          |   |                                                | 08h                 |

|          |   |                                                | 00h                 |

|          |   |                                                | 00h                 |

| 84-85    | М | Number of spare bytes per page                 | 80h                 |

|          |   |                                                | 00h                 |

| 86-89    | М | Number of data bytes per partial page          | 00h                 |

|          |   |                                                | 02h                 |

|          |   |                                                | 00h                 |

|          |   |                                                | 00h                 |

| 90-91    | М | Number of spare bytes per partial page         | 20h                 |

|          |   |                                                | 00h                 |

| 92-95    | М | Number of pages per block                      | 40h                 |

|          |   |                                                | 00h                 |

|          |   |                                                | 00h                 |

|          |   |                                                | 00h                 |

| 96-99    | М | Number of blocks per logical unit (LUN)        | 00h                 |

|          |   |                                                | 10h                 |

|          |   |                                                | 00h                 |

|          |   |                                                | 00h                 |

| 100      | М | Number of logical units (LUNs)                 | 01h                 |

| 101      | М | Reserved                                       | 00h                 |

|          |   |                                                |                     |

| 102      | М | Number of bits per cell                        | 01h                 |

| 103-104  | М | Bad blocks maximum                             | 50h                 |

|          |   |                                                | 00h                 |

| 105-106  | М | Block endurance                                | 05h                 |

|          |   |                                                | 04h                 |

| 107      | М | Guaranteed valid blocks at beginning of target | 01h                 |

| 108-109  | М | Block endurance for guaranteed valid blocks    | 00h                 |

|          |   |                                                | 00h                 |

| 110     | М | Number of programs per page                                                   | 04h         |

|---------|---|-------------------------------------------------------------------------------|-------------|

| 111     | М | Partial programming attributes                                                | 00h         |

|         |   | 5-7 Reserved                                                                  |             |

|         |   | 4 1 = partial page layout is partial page data followed by partial page spare |             |

|         |   | 1-3 Reserved                                                                  |             |

|         |   | 0 1 = partial page programming has constraints                                |             |

| 112     | М | Number of bits ECC correctability                                             | 00h         |

| 113     | М | Number of interleaved address bits                                            | 00h         |

|         |   | 4-7 Reserved (0)                                                              |             |

|         |   | 0-3 Number of interleaved address bits                                        |             |

| 114     | 0 | Interleaved operation attributes                                              | 00h         |

|         |   | 4-7 Reserved (0)                                                              |             |

|         |   | 3 Address restrictions for program cache                                      |             |

|         |   | 2 1 = program cache supported                                                 |             |

|         |   | 1 1 = no block address restrictions                                           |             |

|         |   | 0 Overlapped / concurrent interleaving support                                |             |

| 115-127 |   | Reserved                                                                      | 00h         |

|         |   |                                                                               |             |

|         |   |                                                                               | 00h         |

|         |   | Electrical parameters block                                                   |             |

| 128     | М | I/O capacitance                                                               | 10h         |

| 129-130 | М | IO clock support                                                              | 00h         |

|         |   |                                                                               | 00h         |

|         |   |                                                                               |             |

| 131-132 | 0 | Reserved (0)                                                                  | 00h         |

|         |   |                                                                               | 00h         |

| 133-134 | М | tPROG Maximum page program time (us)                                          | 58h         |

|         |   |                                                                               | 02h         |

| 135-136 | М | tBERS Maximum block erase time (us)                                           | 10h         |

|         |   |                                                                               | 27h         |

| 137-138 | М | tR Maximum page read time (us)                                                | 78h         |

|         |   |                                                                               | 00h         |

| 139-140 | М | Reserved                                                                      | 00h         |

|         |   |                                                                               | 00h         |

| 141-163 |   | Reserved                                                                      | 00h         |

|         |   | Vendor block                                                                  |             |

| 164-165 | М | Vendor specific Revision number                                               | 00h         |

| 166-253 |   | Vendor specific                                                               | 00h         |

| 254-255 | М | Integrity CRC                                                                 | Set on test |

|         |   | Redundant parameter pages                                                     |             |

| 256-511 | М | Value of bytes 0-255                                                          |             |

| 512-767 | М | Value of bytes 0-255                                                          |             |

### **GD5F4GM8UEYIGR-MT**

### Notes:

- 1. "O" Stands for Optional, "M" for Mandatory

- 2. The Integrity CRC (Cycling Redundancy Check) field is used to verify that the contents of the parameters page were transferred correctly to the host. Please refer to ONFI 1.0 specifications for details. The CRC shall be calculated using the following 16-bit generator polynomial:  $G(X) = X^{16} + X^{15} + X^2 + 1$ , This polynomial in hex may be represented as 8005h.

- 3. The CRC value shall be initialized with a value of 4F4Eh before the calculation begins. There is no XOR applied to the final CRC value after it is calculated. There is no reversal of the data bytes or the CRC calculated value.

| Device Model    | ORGANIZATION | VCC RANGE   | CRC value B254/B255 |

|-----------------|--------------|-------------|---------------------|

| "GD5F4GM8UxxxG" | X4           | 2.7v ~ 3.6v | 9Fh/31h             |

# 8.12 Read CASN Page

The Read CASN Page function retrieves the data structure that describes the chip's organization, features, timing and other behavioral parameters. This data structure enables the host processor to automatically recognize the SPI-NAND Flash configuration of a device. The whole data structure is repeated at least three times.

Sequence is as follows (Same as Read Parameter Page):

- 6. Use Set Feature command to set B0 register, to enable OTP\_EN.

- 7. Use Get Feature command to get data from B0 register and check if the OTP\_EN is enable.

- Use Page Read to Cache (13h) command with address 24'h000001h. Load parameter page and CASN page from array to cache.

- 9. Use 0Fh (GET FEATURES command) read the status

- 10. User can use Read from cache command (03h/0Bh), read CASN page from Byte768 to Byte1535.

### CASN page table as follow

| Byte    | Description                                             | 3.3V        |

|---------|---------------------------------------------------------|-------------|

| 768-771 | CASN page signature                                     | 43h         |

|         | Byte 0: 43h, "C"                                        | 4311<br>41h |

|         | Byte 1: 41h, "A"                                        | 53h         |

|         | Byte 2: 53h, "S"                                        | 4Eh         |

|         | Byte 3: 4Eh, "N"                                        | 4EN         |

|         | Revision number                                         |             |

| 772     | bit7~4: major version,                                  | 10h         |

|         | bit3~0: minor version                                   |             |

|         |                                                         | 47h         |

|         |                                                         | 49h         |

|         |                                                         | 47h         |

|         |                                                         | 41h         |

|         |                                                         | 44h         |

|         | Device manufacturer (12 ASCII characters)               | 45h         |

| 773-785 | Device manufacturer (13 ASCII characters)  "GIGADEVICE" | 56h         |

|         |                                                         | 49h         |

|         |                                                         | 43h         |

|         |                                                         | 45h         |

|         |                                                         | 20h         |

|         |                                                         | 20h         |

|         |                                                         | 20h         |

| evice   | SPI-NAI                            | ND GD                      | 5F4GM8UEYIGR-M |

|---------|------------------------------------|----------------------------|----------------|

|         |                                    |                            | 47h            |

|         |                                    |                            | 44h            |

|         |                                    |                            | 35h            |

|         |                                    |                            | 46h            |

|         |                                    |                            | 34h            |

|         |                                    |                            | 47h            |

|         |                                    |                            | 4Dh            |

| 700 004 | Device model (16 ASCII characters) |                            | 38h            |

| 786-801 | "GD5F4GM8UE"                       |                            | 55h            |

|         |                                    |                            | 45h            |

|         |                                    |                            | 20h            |

|         |                                    | 1.5                        | 00h            |

| 000 005 |                                    | bit per cell               | 00h            |